Qucsでシミュレーション

Qucs でシミュレーションをしてみましょう。アナログ回路シミュレーションはアクティブ・ローパス・フィルタで、デジタル回路シミュレーションは3ビットの同期カウンタを例にします。

アナログ回路のシミュレーション

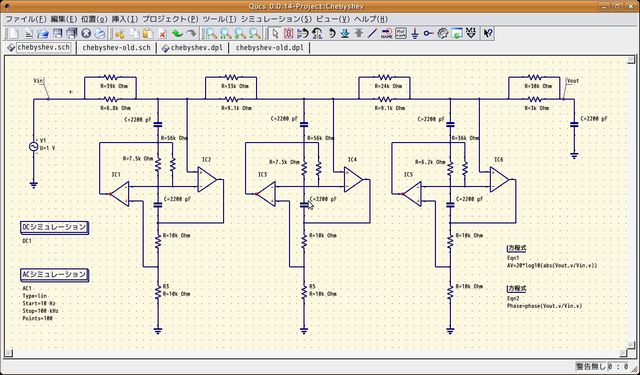

7次のアクティブ・ローパス・フィルタを使用して、ACシミュレーションを実行してゲイン-周波数特性を得ます。

シミュレーションする回路は、LCフィルタのコイルをOPアンプで実現した、FDNR(Frequency Dependent Negative Resistance)と呼ばれる回路です。遮断周波数を20KHzとする、7次のチェビシェフ・ローパス・フィルタです。

余談ですが、20数年前CDプレーヤのDAC出力のアンチエリアシング・フィルタとして、11次の連立チェビシェフ・フィルタが使われていました。FDNR回路は信号が直接、非線形回路を通過しないので音質が良いということで、オペアンプの数は増えコストは上がりますが、良く使っていました。最近はオーバーサンプリングDACなので、このような急峻なフィルタは使われていませんが。

回路入力は直感的に操作できるので、問題ないでしょう。

シミュレーションをするには、「部品」-「シミュレーション部品」から必要なシミュレーション部品をドラッグして回路図上に置きます。部品をダブルクリックすると部品プロパティー編集ウィンドウが開くので、シミュレーション条件等を設定します。

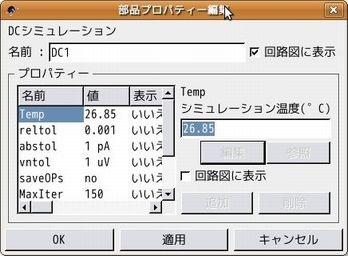

初めに「DCシミュレーション」部品を置きます。ACシミュレーションに先立ってDCバイアスの計算をしますが、これは特になにも設定することはないでしょう。

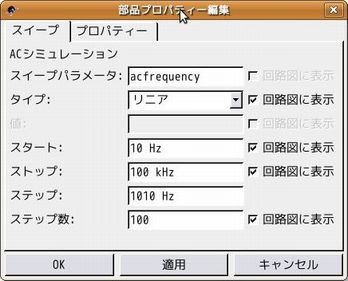

次に「ACシミュレーション」部品を置きます。「ACシミュレーション」部品をダブルクリックし、シミュレーション条件を設定します。

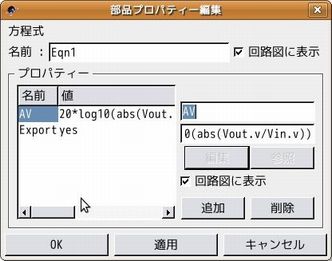

「挿入(I)」メニューから「方程式を挿入」を選択して回路図上に置きます。方程式をダブルクリックし、名前をAVとし、値に20*log10(abs(Vout.v/Vin.v))を入力します。

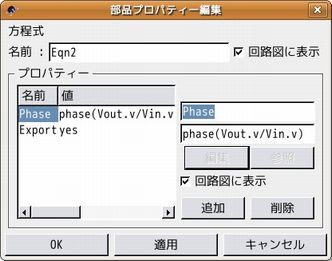

さらに「挿入(I)」メニューから「方程式を挿入」を選択し、名前にPhase、値にPhase(Vout.v/Vin.v)を入力します。

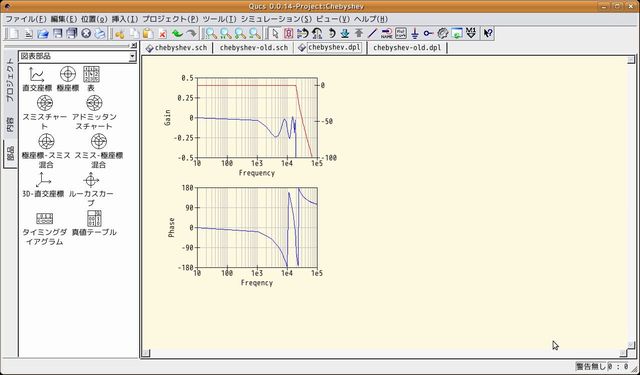

メニューバーの「シミュレーション(S)」メニューから「シミュレート」をクリックするか、シミュレーションアイコンをクリックしシミュレーションを実行します。シミュレーションが成功すると自動的に画面右側にシミュレーション結果のタブが作られ、また左側のタブが「図表部品」に切り替わります。そして、「図表部品」から直交座標を選択して結果を表示させます。

グラフをダブルクリックするとグラフプロパティー編集ウィンドウが開くので、グラフの線の色や軸の名前、グラフ表示の範囲等を変更することができます。

デジタル回路のシミュレーション

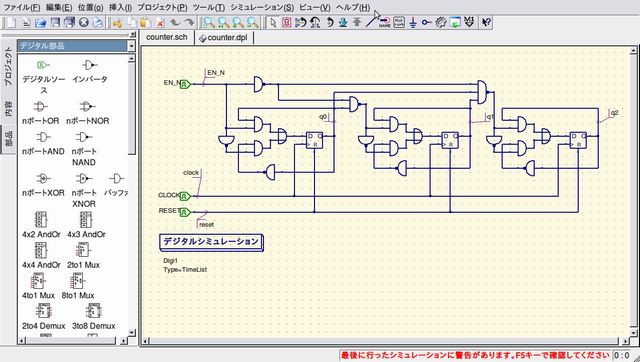

Qucsはデジタル回路のシミュレーションもできます。デジタルシミュレーションするにはフリーのVHDLシミュレータであるFreeHDLがインストールされている必要があります。

ここでは、簡単な3ビットの同期カウンタの回路を設計しシミュレーションしてみます。シミュレーションに使う回路は以下です。観測する信号にはラベルを付けておきます。

回路図上のデジタルソース部品をダブルクリックしてシミュレーション用の入力信号を作成します。

CLOCK信号は初期値を「low」、時間を「50ns; 50ns」とします。

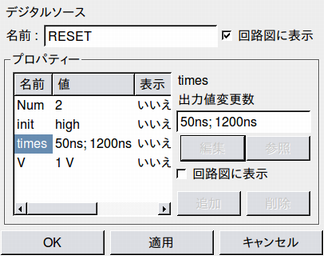

RESET信号は、初期値「high」、時間を「50ns; 1200ns」とします。

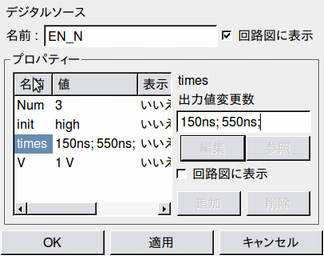

カウントイネーブル信号EN_Nは初期値を「high」、時間を「150ns; 550ns」とします。

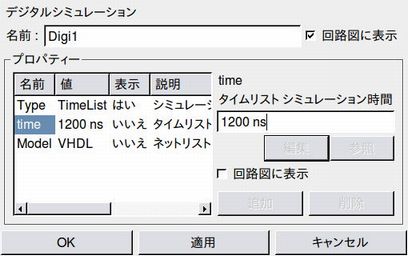

「部品」 - 「シミュレーション部品」からデジタルシミュレーション部品を回路図上に置き、ダブルクリックしてシミュレーション時間の設定をします。

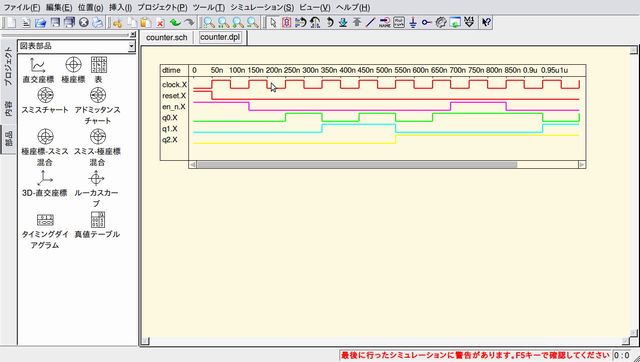

メニューバーの「シミュレーション(S)」メニューから「シミュレート」をクリックするか、シミュレーションアイコンをクリックするとネットリストの作成、コンパイルが実行されます。シミュレーションが成功すると自動的に画面右側にシミュレーション結果のタブが作られ、また左側のタブが「図表部品」に切り替わります。「図表部品」からタイミングダイアグラムをワークエリアにドラッグするとグラフプロパティ編集画面が開くので、「データセット」ボックスから表示させる信号を選択して「グラフ」ボックスに追加します。